- 您现在的位置:买卖IC网 > Sheet目录2003 > LTC1404IS8#TRPBF (Linear Technology)IC A/D CONV 12BIT W/SHTDN 8-SOIC

17

LTC1404

1404fa

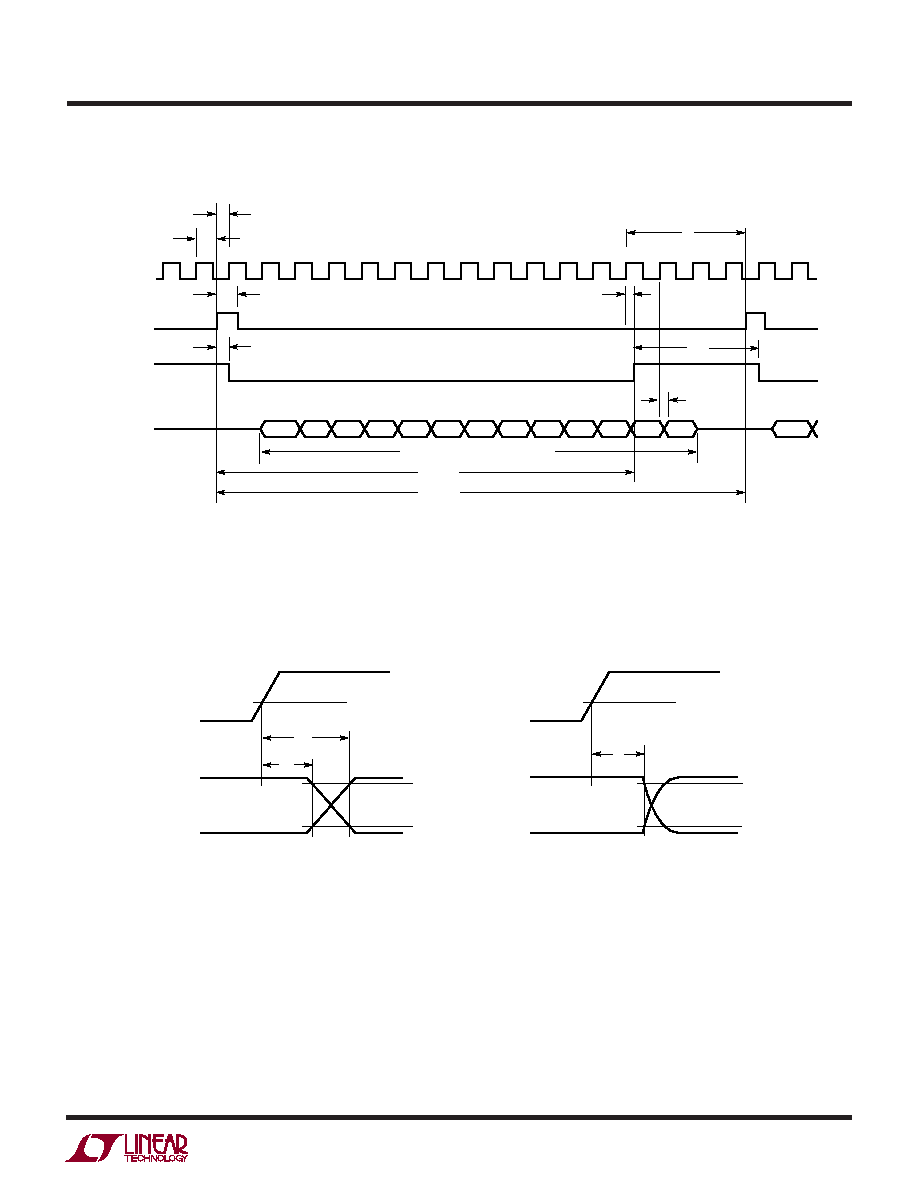

Figure 14. CLK to DOUT Delay

APPLICATIONS INFORMATION

WU

U

CLK

CONV

INTERNAL

S/H STATUS

DOUT

t7

t3

12

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

2

t2

t6

t4

t5

t8

tACQ

SAMPLE

HOLD

REFRDY BIT + 12-BIT DATA WORD

Hi-Z

tCONV

tSAMPLE

1404 F13

REFRDY

D11

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

D10

REFRDY

Figure 13. ADC Digital Timing Diagram

t10

t8

VIH

VOH

VOL

DOUT

CLK

t9

VIH

90%

10%

DOUT

CLK

1404 F14

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

LTC1405IGN#TRPBF

IC ADC 12BIT 5MSPS SAMPLE 28SSOP

LTC1406IGN#TRPBF

IC A/D CONV 8BIT SAMPLING 24SSOP

LTC1407AHMSE#PBF

IC ADC 14BIT 3MSPS 10-MSOP

LTC1407AIMSE-1#TRPBF

IC ADC 14BIT 3MSPS SAMPLE 10MSOP

LTC1408IUH-12#TRPBF

IC ADC 12BIT 600KSPS 32-QFN

LTC1408IUH#TRPBF

IC ADC 14BIT 600KSPS 32-QFN

LTC1409IG#TR

IC ADC 12BIT 800KSPS SMPL 28SSOP

LTC1410IG#TR

IC ADC 12BIT 1.25MSPS SMP 28SSOP

相关代理商/技术参数

LTC1405CGN

功能描述:IC ADC 12BIT 5MSPS SAMPLE 28SSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极

LTC1405CGN#PBF

功能描述:IC ADC 12BIT 5MSPS SAMPLE 28SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6

LTC1405CGN#TR

功能描述:IC ADC 12BIT 5MSPS SAMPLE 28SSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极

LTC1405CGN#TRPBF

功能描述:IC ADC 12BIT 5MSPS SAMPLE 28SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极

LTC1405IGN

功能描述:IC ADC 12BIT 5MSPS SAMPLE 28SSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极

LTC1405IGN#PBF

功能描述:IC ADC 12BIT 5MSPS SAMPLE 28SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:microPOWER™ 位数:8 采样率(每秒):1M 数据接口:串行,SPI? 转换器数目:1 功率耗散(最大):- 电压电源:模拟和数字 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商设备封装:24-VQFN 裸露焊盘(4x4) 包装:Digi-Reel® 输入数目和类型:8 个单端,单极 产品目录页面:892 (CN2011-ZH PDF) 其它名称:296-25851-6

LTC1405IGN#TR

功能描述:IC ADC 12BIT 5MSPS SAMPLE 28SSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极

LTC1405IGN#TRPBF

功能描述:IC ADC 12BIT 5MSPS SAMPLE 28SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极